#### Paper 28.7 – ISSCC2005

# A 3Gb/s AC Coupled Chip-to-Chip Communication using a Low Swing Pulse Receiver

Lei Luo, John M. Wilson, Stephen E. Mick, Jian Xu, Liang Zhang and Paul D. Franzon North Carolina State University, Raleigh, NC

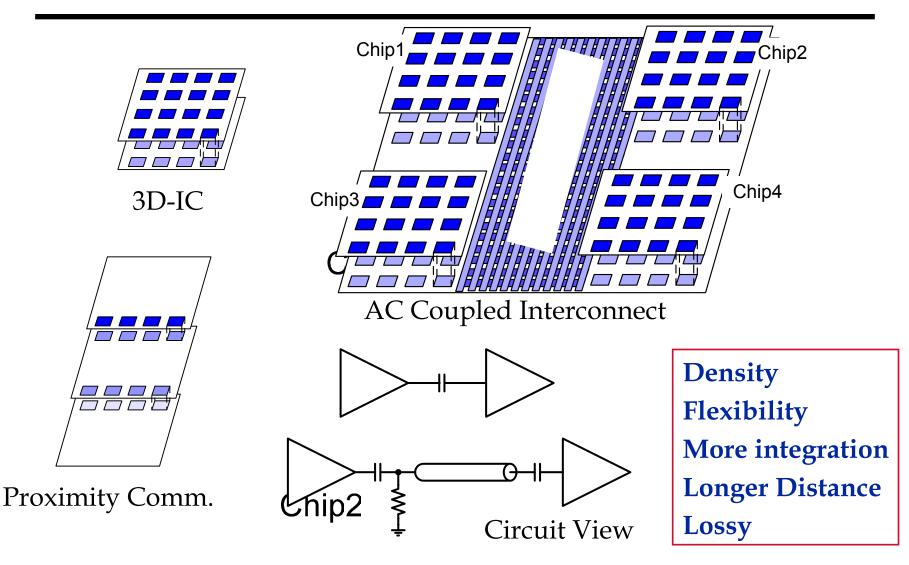

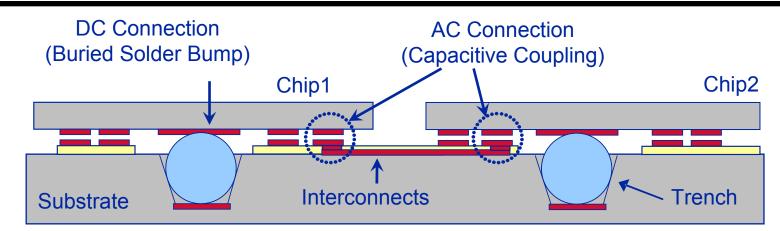

# High density Capacitively Coupled I/Os

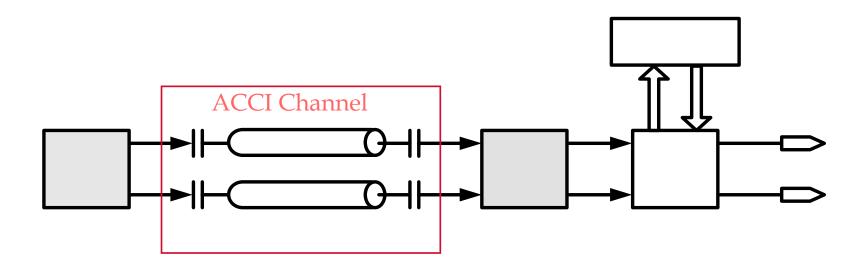

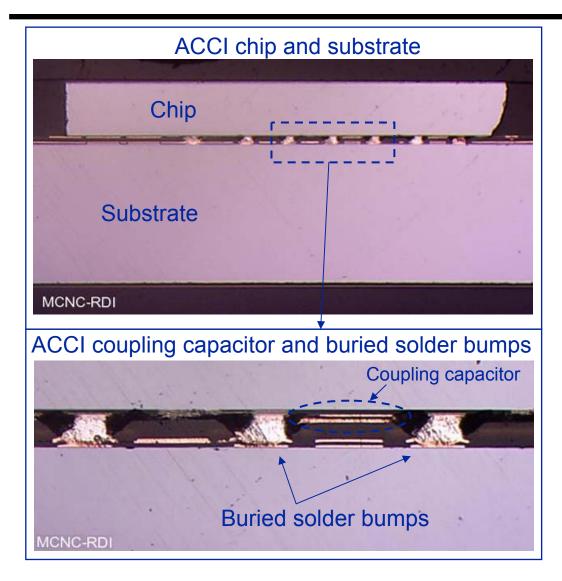

# **AC Coupled Interconnect (ACCI)**

physical structure

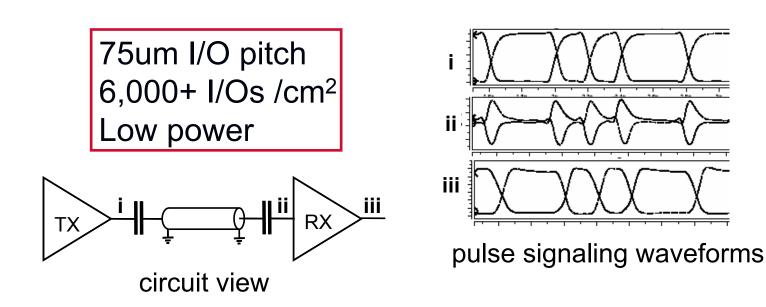

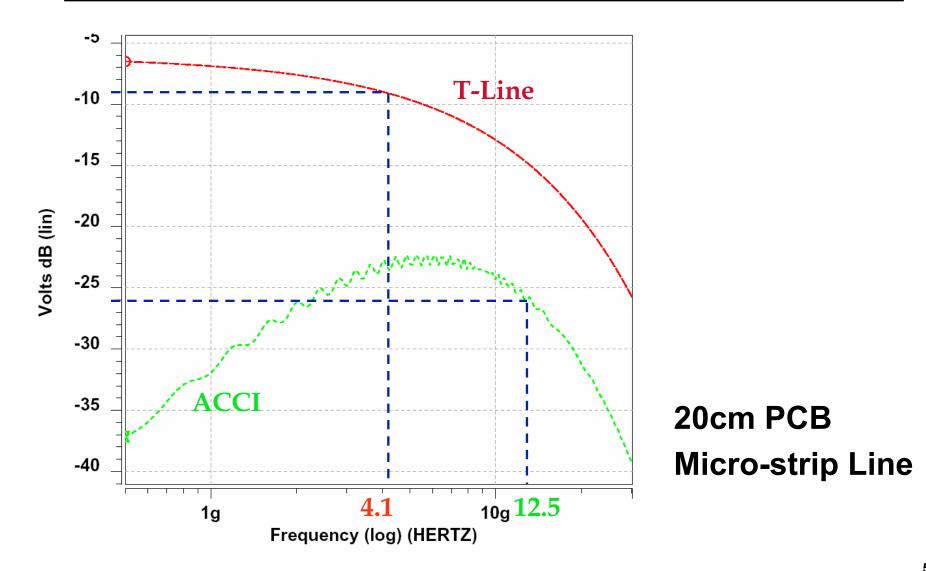

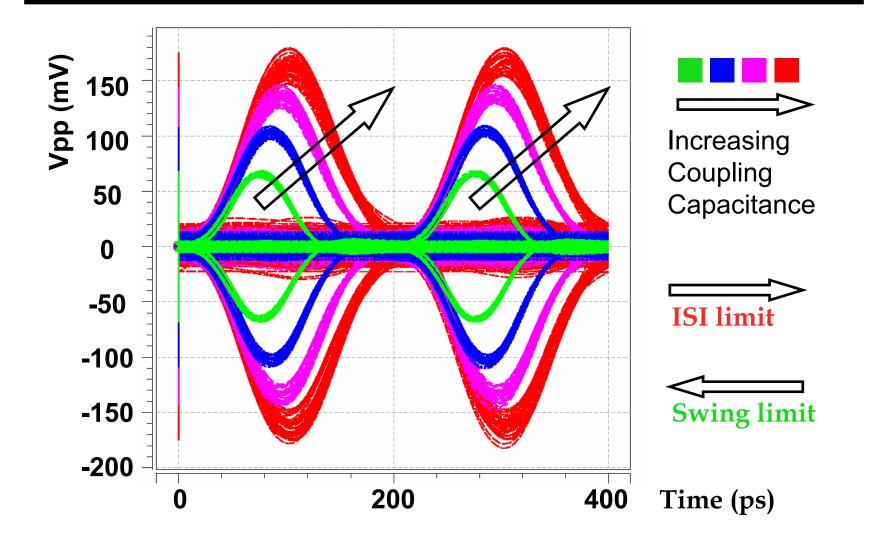

#### **Channel Response**

#### **Expand 3dB bandwidth**

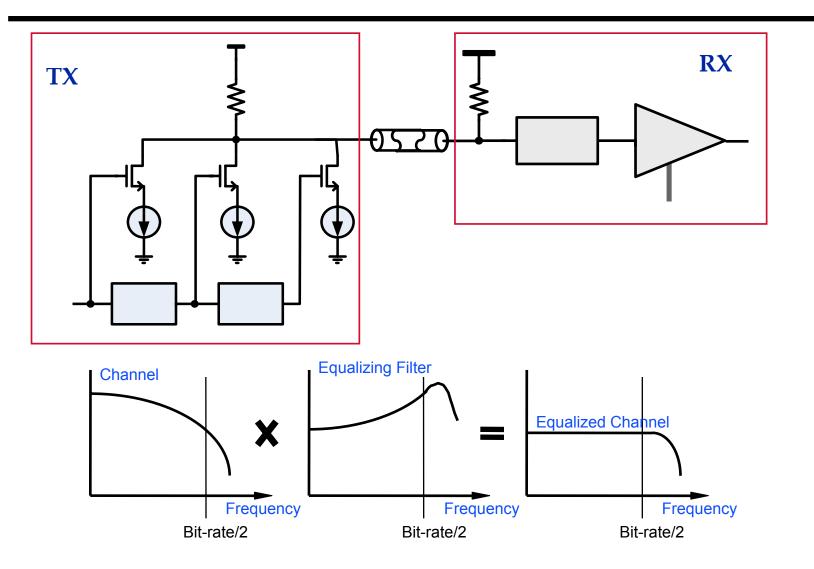

### **Traditional Equalization**

### **ACCI Equalization**

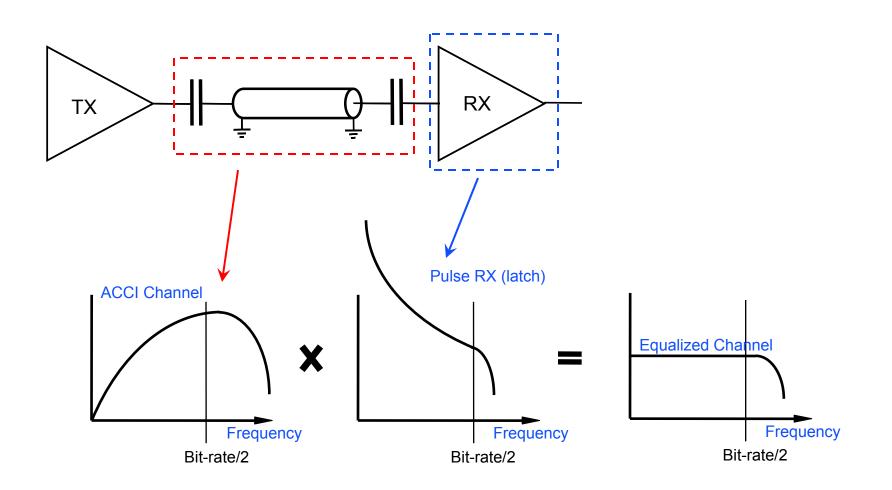

#### **ISI of Pulse Signal**

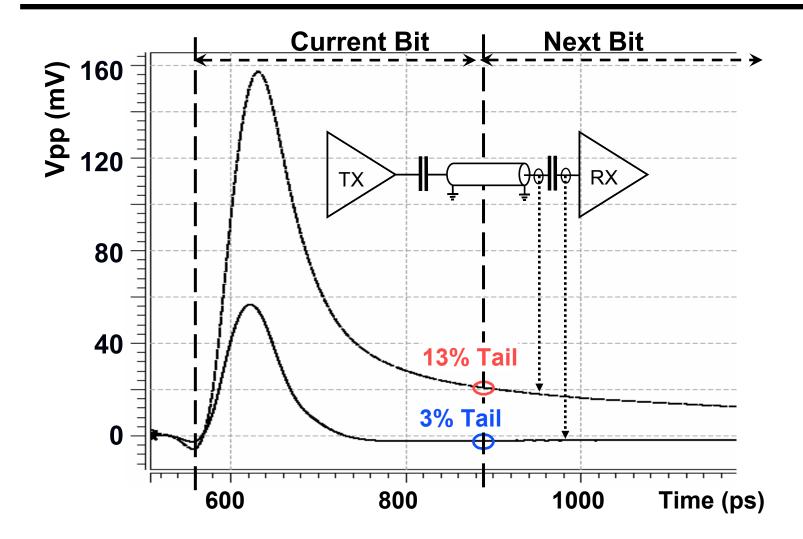

### **EYE at RX input**

# **Components of ACCI**

- ▷ TX outputs NRZ to channel

- Pulse RX converts pulses back to NRZ, then goes to clock and data recovery

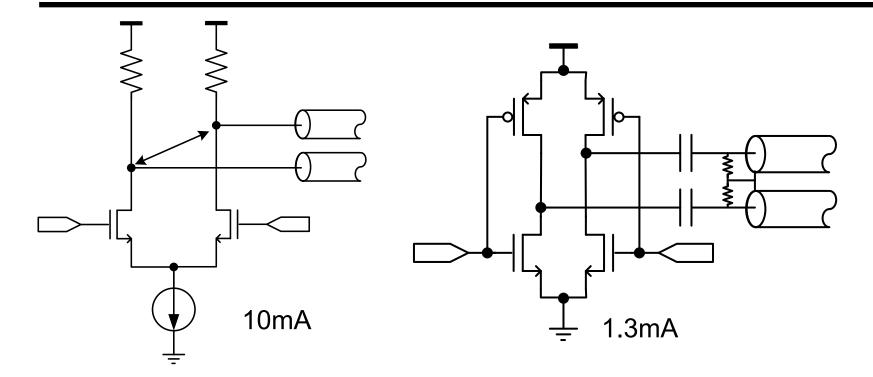

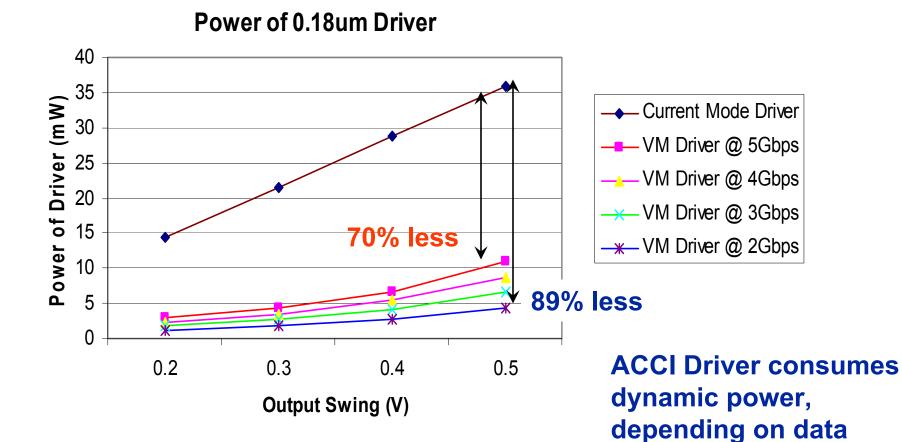

# Low power driver

Current Mode Vs. Voltage Mode

- ◆ 50 ohm TL load Vs. Cap load

- Static current Vs. dynamic current

- 10mA Vs 1.3mA (to get a 0.25V<sub>SEPP</sub> output swing, for 0.18um CMOS)

### **Power Saving**

rate and data activity

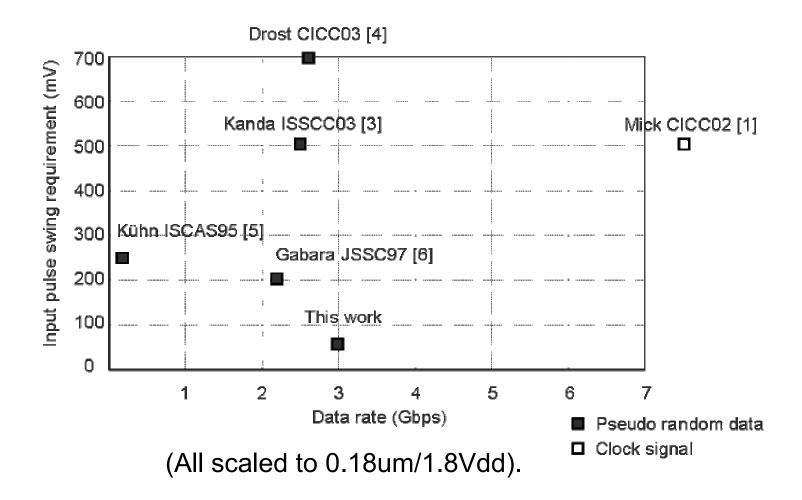

#### **ACCI need sensitive pulse receiver**

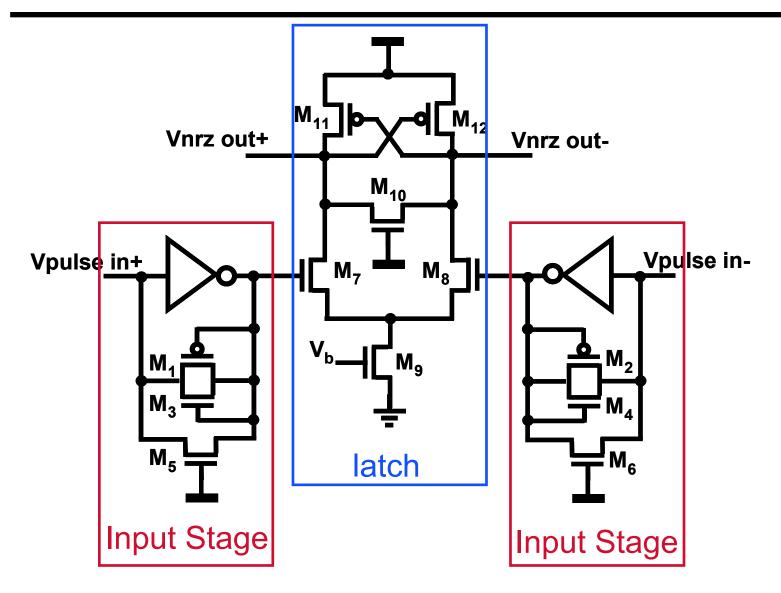

#### A low swing pulse receiver

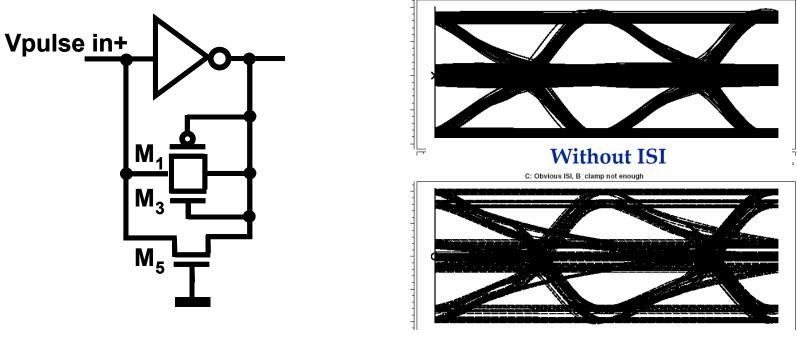

# Input stage

With ISI

- ISI due to limited bandwidth

- ▷ Swing Vs. bandwidth tradeoff → INV and feedback ratio

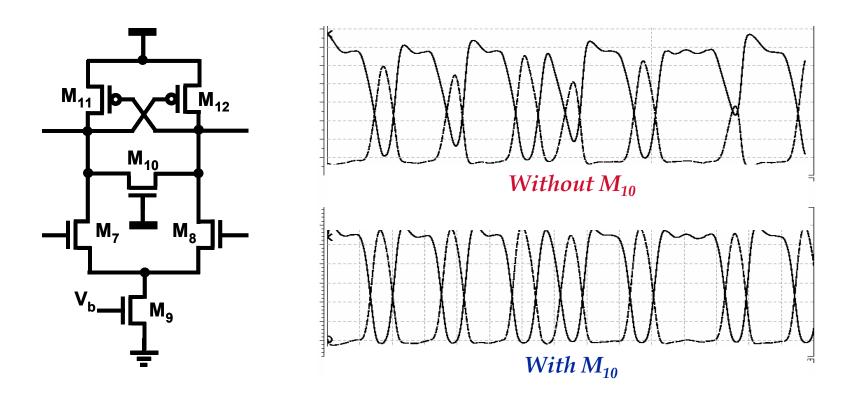

### Latch stage

- Latch : M11 and M12; Edge Detector: M7 and M8

- ▷ Swing and bandwidth tradeoff  $\rightarrow$  M<sub>10</sub>

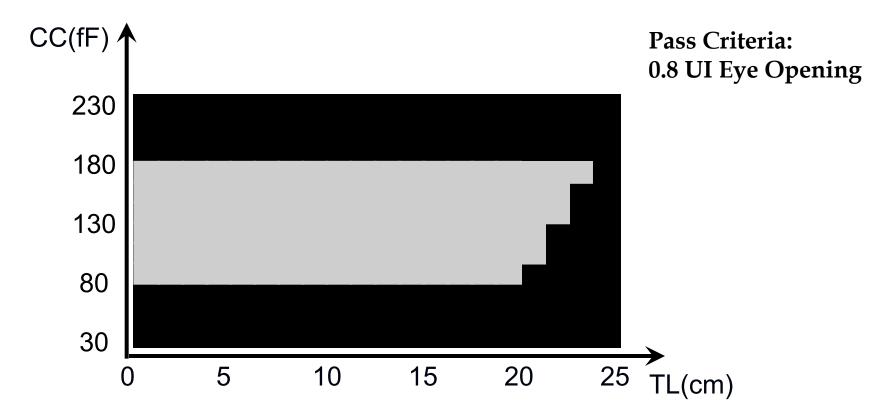

### **Simulated Shmoo Plot**

Works over wide range of Coupling Capacitance, TL Length, up to 3Gb/s

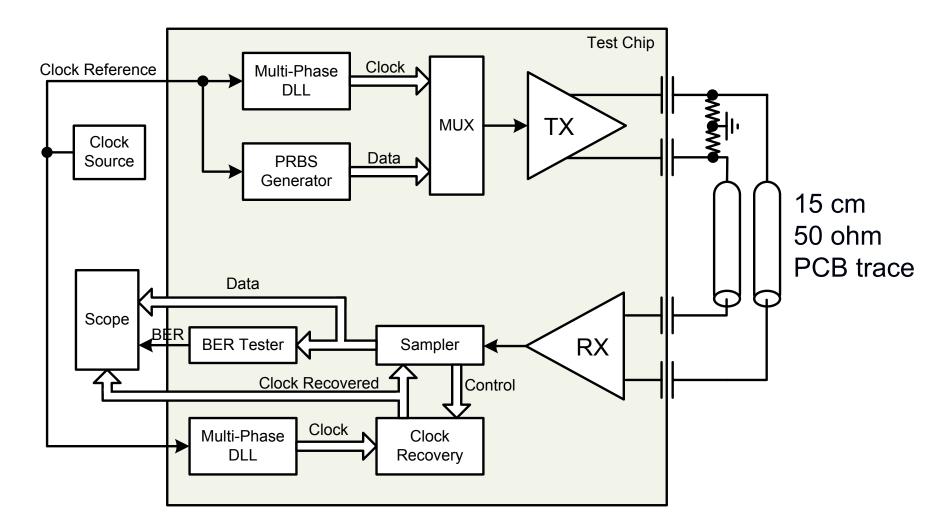

# **Test chip**

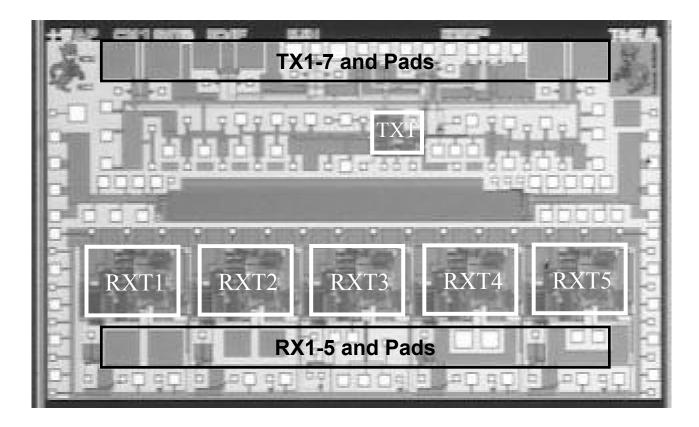

# Die photo

#### TSMC 0.18um CMOS, 2mm by 3.5mm

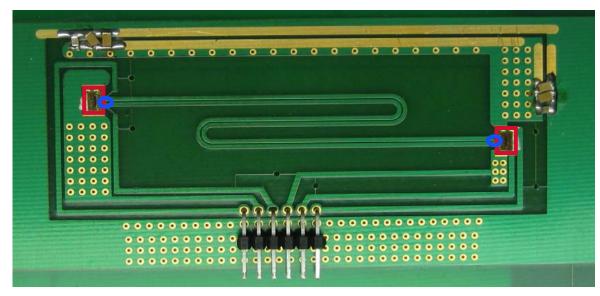

#### **Test Setup on PCB**

15 cm long 50 ohm differential PCB trace

150fF Coupling Capacitors

# **Chip and Measured data**

| Process                |                                       | TSMC 0.18um CMOS 1P 6M          |

|------------------------|---------------------------------------|---------------------------------|

| Supply Voltage         |                                       | 1.8V                            |

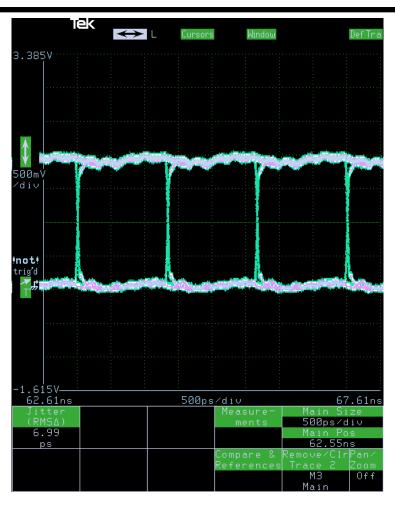

| Data Rate              |                                       | 3Gb/s/channel                   |

| BER                    |                                       | < 10 <sup>-12</sup>             |

| Coupling Caps          |                                       | 60um by 60um on-chip (150fF)    |

| Link                   |                                       | 15cm and 50ohm micro-strip line |

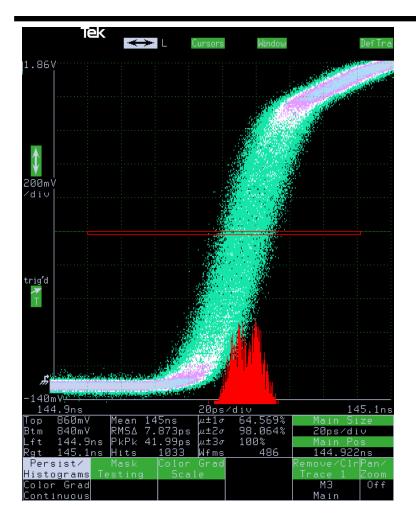

| Jitter of recover data |                                       | 7ps RMS                         |

| Power<br>(mW)          | Driver                                | 5                               |

|                        | Pulse RX                              | 10                              |

|                        | Clock, test<br>circuit and<br>buffers | 116.5                           |

|                        | Total                                 | 134                             |

#### **Recovered Clock and Data**

#### **Recovered Clock**

#### Recovered and Deserialized Data

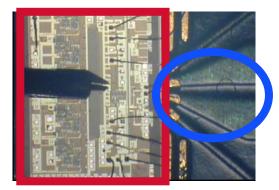

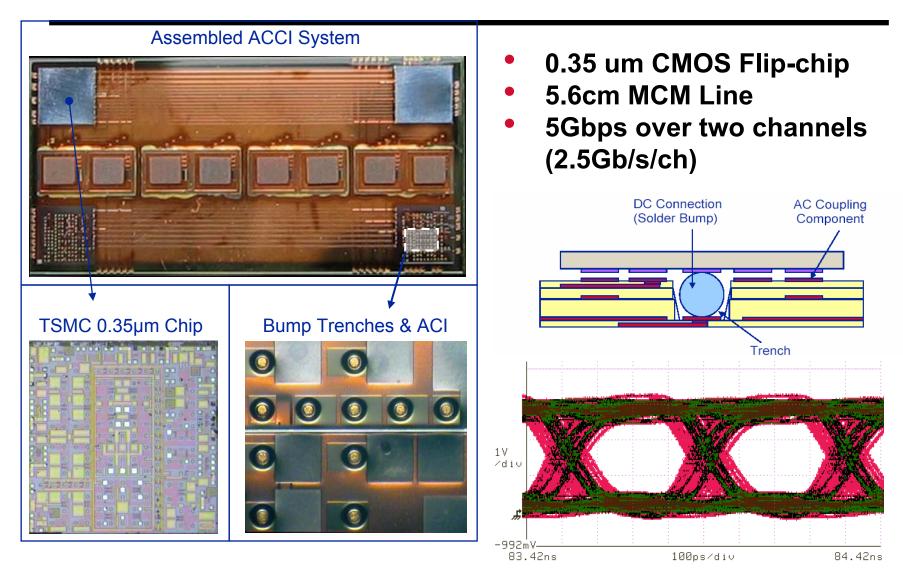

### **MCM-D** Test

# **Substrate / Chip Bonding**

MCM-D fabricated and assembled by MCNC

#### Conclusions

#### AC Coupled interconnect

High density reliable I/Os

Band-pass channel response and Equalization

#### ACCI transceiver

- Voltage mode driver

- A low swing pulse receiver

#### Demonstration

- 15cm TL on PCB

- MCM with 5.6cm TL on BCB substrate